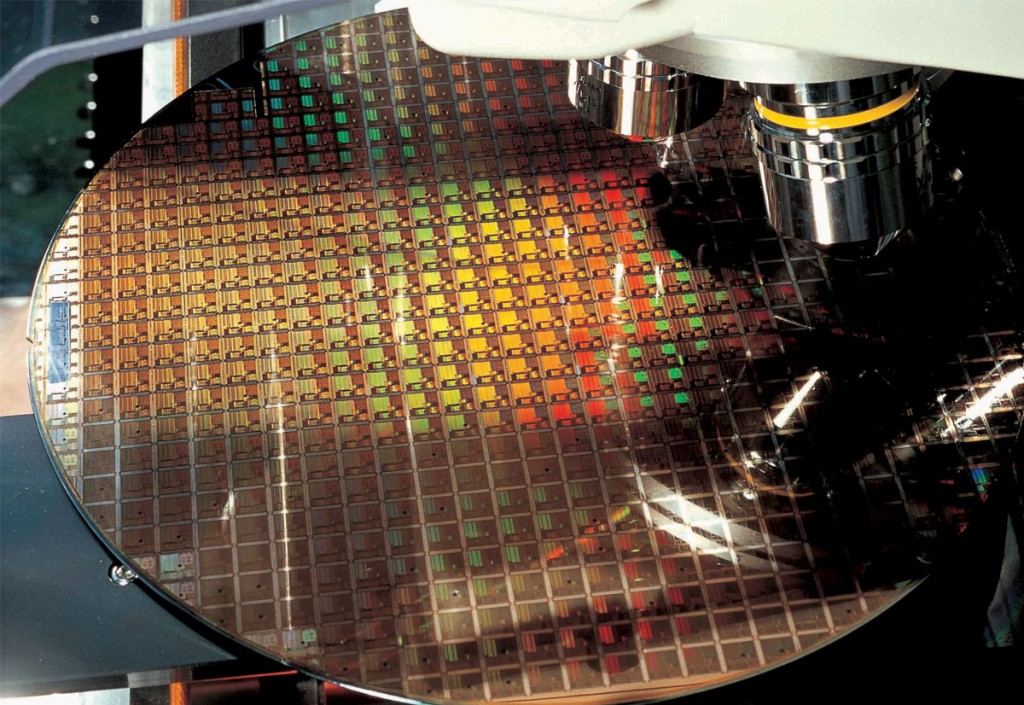

作为知名芯片厂商首选的代工方,台积电(TSMC)身为一家芯片制造业务品牌近年来愈来愈被人们所熟知。由于目前台积电已经开始量产基于7nm工艺制程的移动SoC,预计将有50个产品在今年正式tape-out(下线),我们很快就能目睹它们在性能和功率效率方面相比10nm究竟带来了哪些优势。除了移动SoC外,最近台积电还推出了有望改善显卡性能的晶圆堆叠技术。

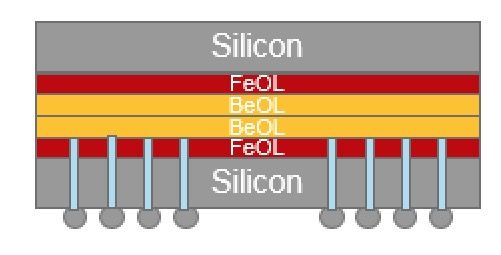

近日在Santa Clara举行的第24届年度技术研讨会上,台积电宣布推出全新的晶圆堆叠(Wafer-on-Wafer,简称WoW)技术,将有望改善DRAM制造和GPU性能。顾名思义,该技术通过硅通孔(TSV)互连将多层逻辑堆叠在一起,由于晶圆上的侧面空间有限,WoW技术将能够使用高速和低延迟互连将能够在同等的空间量塞入更高密度的芯片。

由于目前WoW技术的成品率还很低,因此台积电预计将先在成熟的16nm或10nm工艺部件上进行初步推广。随着技术成熟和产量提高,未来GPU制造商将可以把两个功能齐全的GPU堆叠在一起,从而推出更小更节能的显卡,不用再使用两个独立芯片进行双GPU设置。

在会议上,台积电还宣布了一款采用远紫外(EUV)光刻技术的新7nm +制程将会在2019年上半年推行,而新一代的5nm制程也同样在2019年上半年开始进行“风险生产”。而早在2018年1月份的时候台积电就也开始计划在台湾建设一座全新的5nm晶圆厂,预计将于2020年开始批量生产。

更多Zing彩:

- SAMSUNG 7NM芯片技术提前半年完工:与台积电的订单之争

- 采用台积电7NM制程,HUAWEI KIRIN 980处理器将于本季度开始量产

- 采用7NM工艺打造!曝台积电将独家代工新一代IPHONE的A12处理器

本文:

5nm制程有望明年试产,台积电公布全新晶圆堆叠技术有望为显卡性能带来全新变革

Source :